In 1965 formuleerde Intel-medeoprichter Gordon Moore wat later bekend zou worden als "de wet van Moore". Meer dan een halve eeuw lang lag deze wet ten grondslag aan de gestage verbetering van de prestaties van geïntegreerde schakelingen (IC's) en de dalende kosten – de basis van de moderne digitale technologie. Kort gezegd: het aantal transistors op een chip verdubbelt ruwweg elke twee jaar.

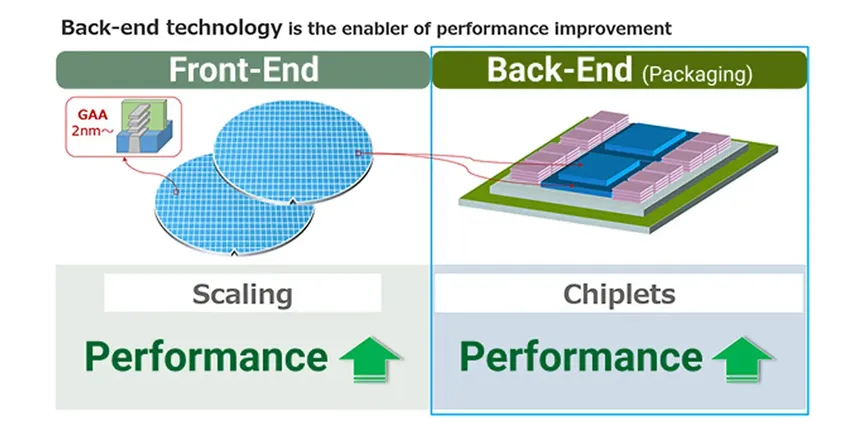

Jarenlang volgde de vooruitgang dat tempo. Nu verandert het beeld. Verdere verkleining is lastiger geworden; de afmetingen van de onderdelen zijn teruggebracht tot slechts enkele nanometers. Ingenieurs lopen tegen fysieke limieten aan, complexere processtappen en stijgende kosten. Kleinere geometrieën drukken ook de opbrengst, waardoor massaproductie moeilijker wordt. Het bouwen en exploiteren van een toonaangevende fabriek vereist enorm veel kapitaal en expertise. Velen beweren daarom dat de Wet van Moore aan kracht verliest.

Die verschuiving heeft de weg vrijgemaakt voor een nieuwe aanpak: chiplets.

Een chiplet is een kleine chip die een specifieke functie uitvoert – in feite een deel van wat vroeger één monolithische chip was. Door meerdere chiplets in één behuizing te integreren, kunnen fabrikanten een compleet systeem samenstellen.

In het monolithische tijdperk bevonden alle functies zich op één grote chip, waardoor een defect waar dan ook de hele chip onbruikbaar kon maken. Met chiplets worden systemen gebouwd met behulp van "bekende-goede chips" (KGD), wat de opbrengst en de productie-efficiëntie aanzienlijk verbetert.

Heterogene integratie – het combineren van chips die op verschillende procestechnologieën zijn gebouwd en voor verschillende functies – maakt chiplets bijzonder krachtig. Krachtige rekenblokken kunnen gebruikmaken van de nieuwste technologietechnologieën, terwijl geheugen en analoge circuits gebaseerd blijven op beproefde en kosteneffectieve technologieën. Het resultaat: hogere prestaties tegen lagere kosten.

De auto-industrie is er bijzonder in geïnteresseerd. Grote autofabrikanten gebruiken deze technieken om toekomstige SoCs voor in de auto te ontwikkelen, met als doel massale toepassing na 2030. Chiplets stellen hen in staat om AI en grafische toepassingen efficiënter op te schalen en tegelijkertijd de opbrengst te verbeteren, waardoor zowel de prestaties als de functionaliteit van halfgeleiders voor de automobielindustrie worden verhoogd.

Sommige auto-onderdelen moeten voldoen aan strenge functionele veiligheidsnormen en zijn daarom afhankelijk van oudere, beproefde technologieën. Moderne systemen zoals geavanceerde rijhulpsystemen (ADAS) en softwaregestuurde voertuigen (SDV's) vereisen daarentegen veel meer rekenkracht. Chiplets overbruggen die kloof: door microcontrollers van veiligheidsklasse, groot geheugen en krachtige AI-acceleratoren te combineren, kunnen fabrikanten SoCs sneller afstemmen op de behoeften van elke autofabrikant.

Deze voordelen reiken verder dan de auto-industrie. Chiplet-architecturen vinden hun weg naar AI, telecommunicatie en andere domeinen, waardoor innovatie in diverse sectoren wordt versneld en ze snel een pijler van de halfgeleiderroadmap worden.

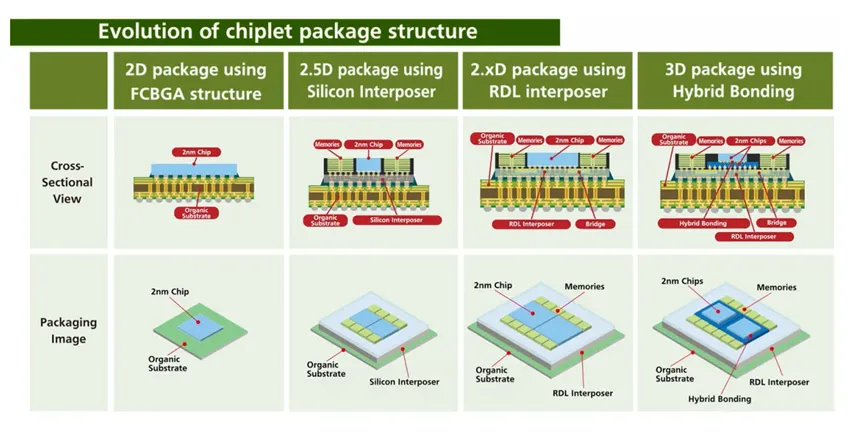

De integratie van chiplets is afhankelijk van compacte, snelle verbindingen tussen de chips. De belangrijkste factor hierbij is de interposer: een tussenlaag, vaak van silicium, onder de chips die signalen doorstuurt, net als een kleine printplaat. Betere interposers betekenen een sterkere koppeling en een snellere signaaloverdracht.

Geavanceerde verpakkingstechnieken verbeteren ook de stroomvoorziening. Dichte opeenvolgingen van minuscule metalen verbindingen tussen de chips zorgen voor voldoende paden voor stroom en data, zelfs in krappe ruimtes. Dit maakt gegevensoverdracht met hoge bandbreedte mogelijk en zorgt voor een efficiënt gebruik van de beperkte ruimte in de verpakking.

De gangbare aanpak van vandaag is 2,5D-integratie: het naast elkaar plaatsen van meerdere chips op een interposer. De volgende stap is 3D-integratie, waarbij chips verticaal op elkaar worden gestapeld met behulp van through-silicon vias (TSV's) voor een nog hogere dichtheid.

Door modulair chipontwerp (waarbij functies en circuittypen gescheiden worden) te combineren met 3D-stapeling ontstaan snellere, kleinere en energiezuinigere halfgeleiders. De combinatie van geheugen en rekenkracht zorgt voor een enorme bandbreedte voor grote datasets – ideaal voor AI en andere veeleisende workloads.

Verticaal stapelen brengt echter uitdagingen met zich mee. Warmte hoopt zich sneller op, wat thermisch beheer en de opbrengst bemoeilijkt. Om dit aan te pakken, ontwikkelen onderzoekers nieuwe verpakkingsmethoden die beter bestand zijn tegen thermische beperkingen. Desondanks is er een sterke dynamiek: de convergentie van chiplets en 3D-integratie wordt algemeen beschouwd als een baanbrekend paradigma – klaar om het stokje over te nemen waar de Wet van Moore ophoudt.

Geplaatst op: 15 oktober 2025